Chip-Package-Board-Systemsimulation

Modellieren Sie Signal- und Power-Integrity vom Chip über das Package bis zur Leiterplatte in einer einzigen EM-Umgebung.

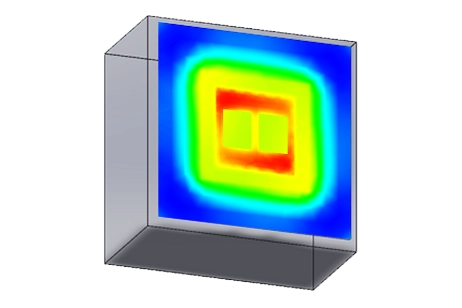

EMV-Simulation einer Intel-CPU mit einem Kühlkörper

Simulation der elektromagnetischen Verträglichkeit einer Dual-Die-CPU mit und ohne Kühlkörper.

Hochfrequenzsimulation eines Through-Silicon Via (TSV) für 3D-Chips mit HFWorks for Solidworks

Hochfrequenzsimulation eines Through-Silicon Via (TSV) für 3D-Chips mit HFWorks for Solidworks