DDR5

DDR5 technology boosts memory performance across various applications, from gaming PCs to data centers and AI systems. Yet, DDR5 implementation poses design hurdles. High data rates amplify signal integrity issues like crosstalk and noise, threatening data accuracy. Moreover, increased power consumption and heat generation demand meticulous thermal management. Electromagnetic simulation tools empower engineers to model DDR5 behavior, fine-tune signal paths, minimize crosstalk, and optimize thermal solutions. These simulations ensure DDR5 systems perform at their best, overcoming inherent challenges in this advanced technology.

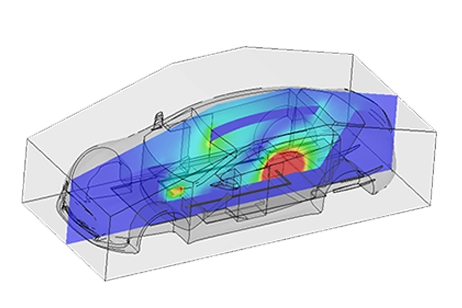

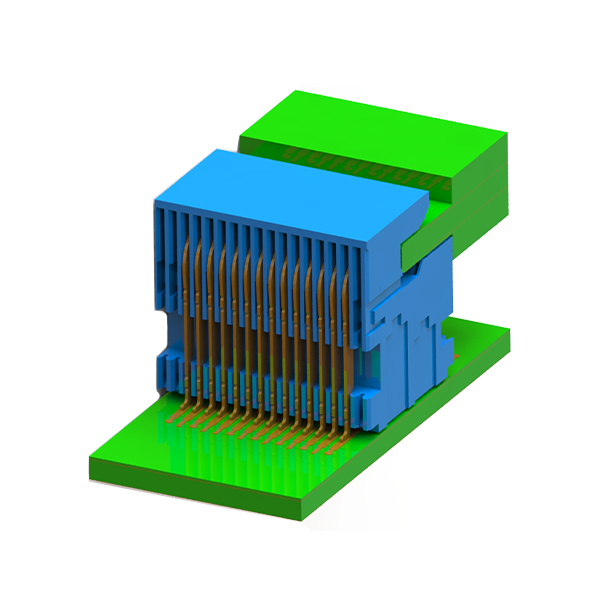

Proposed DDR5 Connector

The connector design features an FR4 board alongside a housing composed of material with a permittivity of 3.9 and a loss tangent of 0.004.

Fig.1. DDR5 Connector

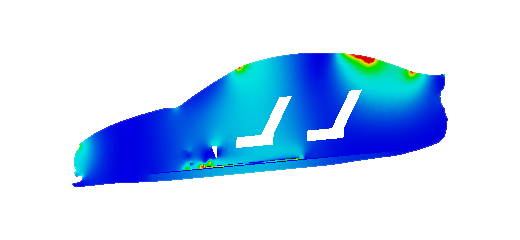

Fig. 2. E-Field Animation (10.25 GHz)

Crosstalk and Noise

Higher frequencies and denser routing on PCBs can amplify crosstalk among neighboring traces, potentially causing signal interference and data inaccuracies. Implementing best practices like adequate trace spacing and differential signaling methods is crucial to minimize crosstalk effects.

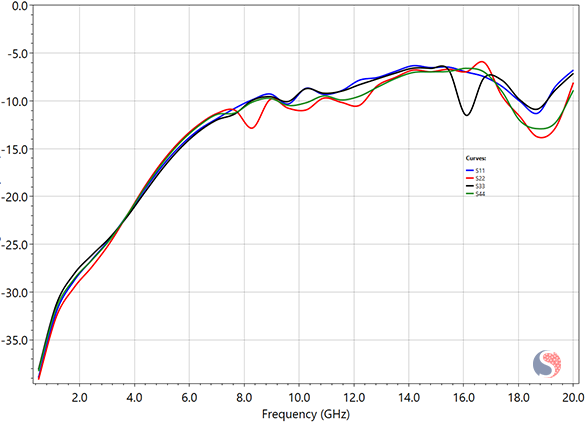

Fig. 3. Return Loss of DDR5 Connector

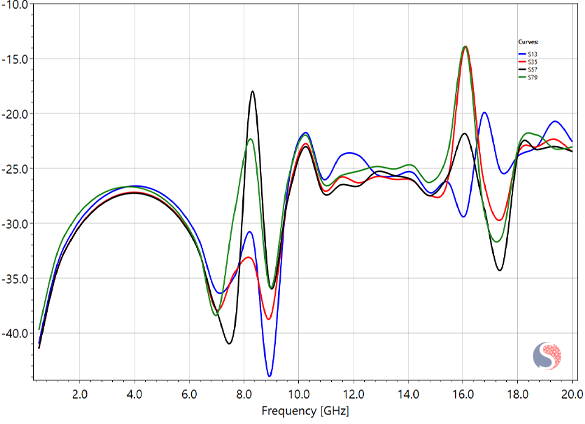

Fig. 4. Insertion Loss of DDR5 Connector

As illustrated in the figures above, the connector demonstrates excellent performance up to 11 GHz. Signal traces maintain effective isolation from DC to 11 GHz, exhibiting an insertion loss of less than -20 dB.

Signal Integrity and Loss

With rising data rates, the impact of signal loss intensifies, primarily attributed to trace impedance mismatch, dielectric losses, and skin effect.

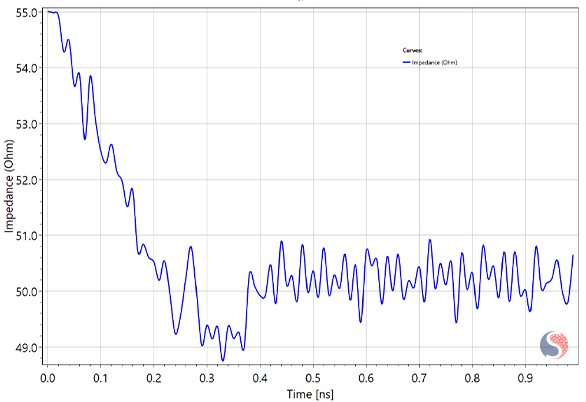

Fig. 5. TDR (Port1)

The TDR plot consistently demonstrates controlled impedance profiles over time, underscoring the importance of maintaining such traces to prevent signal degradation. Minimizing losses is imperative to ensure reliable communication between memory modules and the controller.

Thermal Considerations

Higher data rates in DDR5 memory modules can elevate power consumption and subsequent heat generation, necessitating efficient thermal management strategies to prevent overheating and ensure stable operation. Implementing measures such as heat sinks, thermal vias, and optimized airflow can effectively dissipate heat and maintain optimal operating temperatures.

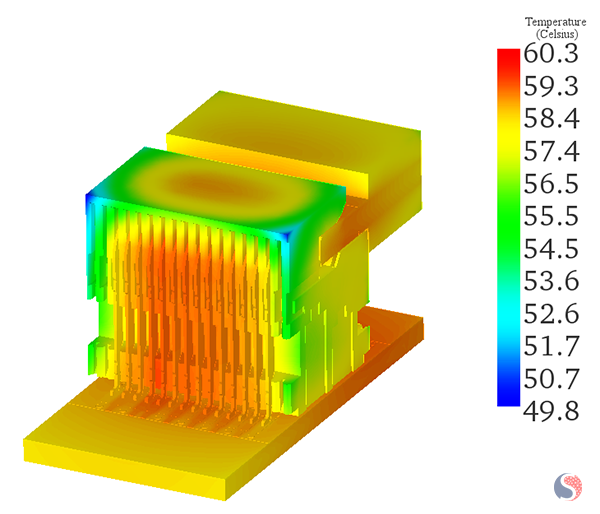

Fig. 6. Temperature (10.25 GHz)

Analyzing the temperature distribution of the connector reveals that it reaches a maximum temperature of 60.3°C at 10.25 GHz, well within the established standard limits.

Conclusion

In summary, DDR5 technology offers significant performance enhancements across various applications, yet its implementation presents design challenges. Electromagnetic simulation tools prove invaluable in optimizing DDR5 systems by fine-tuning signal paths, minimizing crosstalk, and optimizing thermal solutions. The proposed DDR5 connector design demonstrates robust performance, effectively managing signal integrity and thermal dissipation. With careful consideration and simulation-driven design, engineers can ensure the reliable and efficient operation of DDR5 memory modules.

References

[1] https://ieeexplore.ieee.org/document/8401666

[2] https://ieeexplore.ieee.org/document/9994998