はじめに

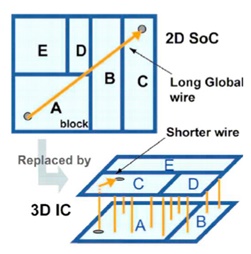

シリコン貫通ビア (TSV) を使用した 3 次元相互接続は、最新のチップで帯域幅を拡大し、待ち時間を短縮し、消費電力を削減するために開発されました。それらは、基板を介して直接ダイスタックの異なる層を接続する目的を果たします。 TSV の一般的な寸法は、直径が 5 ~ 150 µm、ビアの長さが 20 ~ 200 µm の範囲です。図 1 に示すように、TSV の利用により、効率的な相互接続技術が可能になり、従来のワイヤ ボンディング技術と比較して、よりコンパクトなチップ設計とパッケージングが可能になります。

3D IC スタッキングは、熱とコストの問題からメモリ センサーやイメージ センサーではあまり使用されていませんが、ザイリンクスは TSV ベースのシリコン インターポーザーを採用して、2.5D アーキテクチャを使用した 28 Gbps フィールド プログラマブル ゲート アレイ (FPGA) システムを実証しました。

この記事では、Solidworks 内の HFWorks と呼ばれる数値シミュレーターを使用して単一の TSV を分離することにより、シリコン貫通ビア (TSV) のパフォーマンスをモデル化し、評価します。シリコン貫通ビアは、Solidworks で設計され、HFWorks の S パラメータ解析を使用してシミュレートされます。

設計とシミュレーション

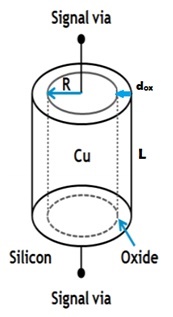

図 2 は、Solidworks で設計された TSV コネクタを示しています。このアプリケーションは、HFWorks 環境のエアボックスに囲まれたシリコン ボックス内の TSV で構成されています。シリコン ボックスは、抵抗率が 10Ω.cm になるように選択されています。実装された TSV は、長さ 50 μm、断面直径 5 μm の銅棒です。

図 1 - 2D IC と 3D IC のワイヤ接続の比較。

TSV を基板から絶縁するために、厚さ 0.5 μm の二酸化シリコン層で覆われています。 TSV の上部と下部のプレートは、50 オームのインピーダンスで励起を適用するためのウェーブ ポートとして選択されます。

![]()

図 2 -スルー シリコン ビア TSV の 3D Solidworks モデル。

コネクタ TSV の概略図を図 3 に示し、幾何学的パラメータ、使用材料を表 1 にまとめます。

図 3 -単一の TSV の回路図ダイガラム

表1 - コネクタの寸法詳細

| パラメーター | 値 | 部品 | 材料 |

| R | 2.5?m | TSV body | 銅 |

| dox | 0.5?m | Dielectric | 二酸化ケイ素 |

| L | 50?m | Silicon box | ケイ素 |

| Air Box | 空気 |

結果

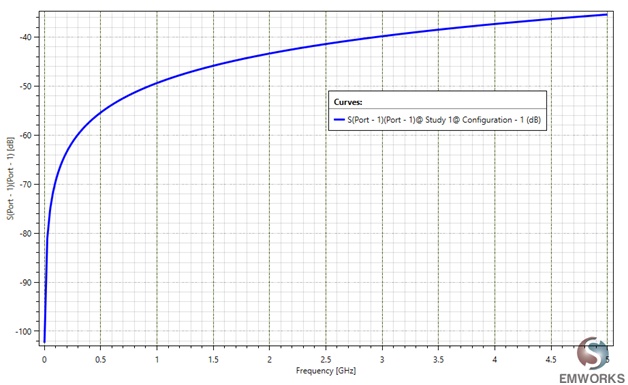

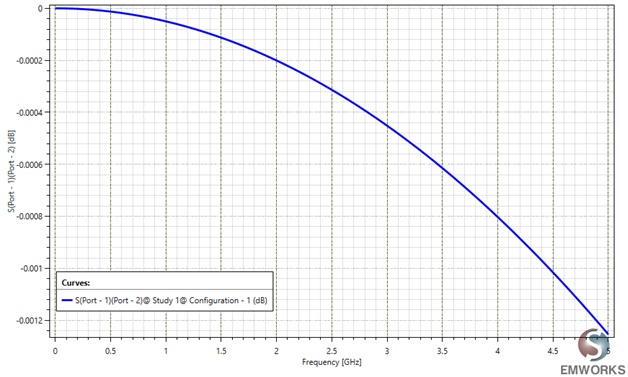

S パラメータ S11 の変化を図 4 に示します。予想通り、高周波でわずかな挿入損失を示します。これは主に、構造内の 3 つの基本モード、つまり遅波モード、誘電準 TEM モード、および表皮効果モードの存在によるものです。急な傾きは、徐波モードから準 TEM モードへの移行を示しています。

図 4 -シングル TSV のリターン ロス S11

図 5 の挿入損失 S21 グラフは、入力信号が 1 GHz で 0.00005 dB 未満だけ減衰することを示しています。 S21 が 0 に近いと予想されるため、これは比較的良い結果です。

図 5 -シングル TSV の挿入損失 S21

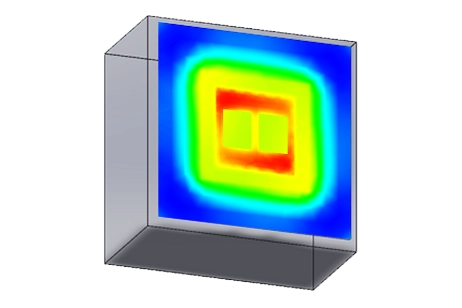

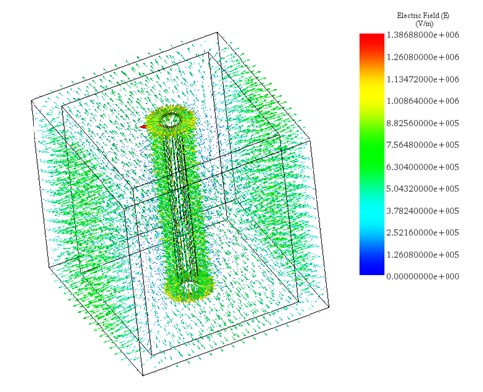

1 GHz での電界の分布を図 6 に示します。明らかに、電界は、基板内の欠陥のない TSV に沿って均一に分布しています。

図 6 -単一の TSV の 1 GHz での電界の分布

結論

この記事では、Solidworks 用の HFWorks に実装された 3D スルー シリコン ビア (TSV) 構造を紹介します。挿入損失、リターン損失、および電界分布は、HFWorks の S パラメータ スタディを使用して決定されました。 HFWorks で得られた結果は、参考文献 [1] に示されている期待値と一致しています。

参考文献

[1] Gong, Zheng, "TSV Equivalent Circuit Model using 3D Full-Wave Analysis" (2014). Electronic Theses and Dissertations. Paper 5238.