電磁適合性 EMC/EMI は、最近、電子およびチップの設計者にとって重要になっています。このパラダイム シフトは、主にチップの密度と周波数の増加、および供給電圧の低下によるものです。逆説的に言えば、特にヒートシンクが設計に存在する場合、チップは文字通り、大量の電磁エネルギーを放射するアンテナのようになっています。典型的なデバイスは、各ダイに 2 つのコア、同じパッケージに 2 つのダイ、そしてもちろんヒートシンクを備えたインテル クアッド コア プロセッサです。

この記事では、HFWorks と SolidWorks のデュオを使用して、ISM 無線帯域、つまり 2.05 GHz と 4.9 GHz の周波数で Intel デュアル ダイ CPU の EMC の側面を調査する方法を紹介します。リターン ロス (S11)、近距離、遠距離、電磁場などの電気的結果が表示され、実際の測定値と比較されます。温度分布と温度勾配を含む熱結果も、ヒートシンクの有無にかかわらず表示されます。

Dual Die CPUのシミュレーション

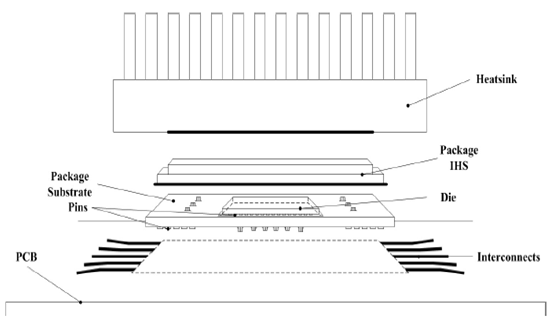

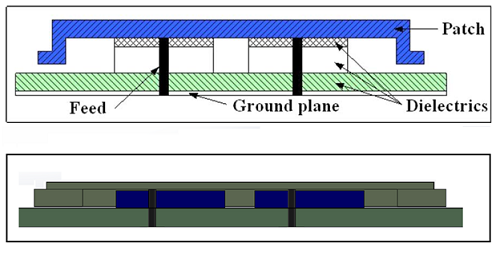

図 1 は、研究対象の Intel デュアル ダイ プロセッサの横断面とヒートシンクをパッケージ構造、相互接続、PCB インフラストラクチャと共に示しています。この調査では、チップの複雑な内部相互接続は無視され、図 2 に示すように、構造のストリップ バージョンのみが考慮されます。ここでは、デュアル プロセッサが 2 つの同軸フィードを備えたマイクロストリップ パッチ アンテナとしてモデル化されています。実際、剥ぎ取られたモデルはチップの実際の構造に似ています。

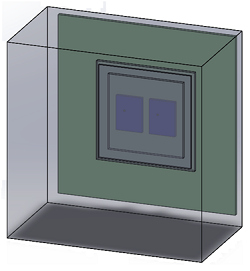

実際の集積回路のピンと相互接続は、図 1 と図 2 に示すように、2 つの同軸フィードとしてモデル化されています。したがって、フィードの位置は、想定されるモデルの全体的なパフォーマンスをほぼ形成するため、慎重に設計する必要があります。シミュレーションで使用された寸法と材料特性を表 1 と 2 に示します。構造とその周囲の空気領域の Solidworks モデルを図 3 に示します。

| 名前 | 標準 (mm) |

|---|---|

| Height of Heatsink HH | 変数 |

| Height of IHS | 1.65 |

| Height of Die | 1.15 |

| Height of substrate | 1.25 |

| Depth of TIM | 0.1 |

| Depth of Die attach material | 0.1 |

| IHS シーラントの深さ | 0.1 |

| Depth of IHS Sealant | 67.5 |

| Width of Heatsink | 67.5 |

| Length of Die | 11.9 |

| Width of Die | 9.0 |

| Length of substrate | 37.5 |

| Width of substrate | 37.5 |

| Length of IHS External | 34 |

| Width of IHS External | 34 |

| Length of IHS Internal | 26 |

| Width of IHS Internal | 26 |

| 名前 | 材料 | 誘電率 | 導電率(シーメンス/m) |

|---|---|---|---|

| Substrate | FR4エポキシ | 4.4 | 0 |

| Die | 二酸化ケイ素 | 4 | 0 |

| IHS | アルミニウム | 1 | 3.8×10 7 |

| Heatsink | アルミニウム | 1 | 3.8×10 7 |

| TIM | シリコーン | 1.8 | 0 |

| Die attach material | 銀 | 1 | 6.1x10 7 |

| IHS Sealant | エポキシ | 1.8 | 0 |

CPU のアンテナ モデルは、インピーダンスが の 2 つの円形 wave ポートを介して励起されます。ポートは基板の下部にあり、IHS と接触する 2 つの銅同軸フィードに接続されています [1]。

図 3 -ヒートシンク付きインテル デュアル ダイ CPU プロセッサの 3D モデル

シミュレーションと結果

A. ヒートシンクの効果

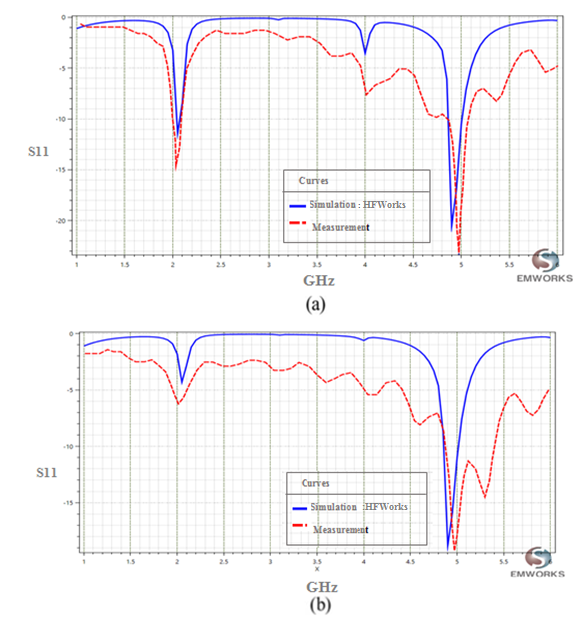

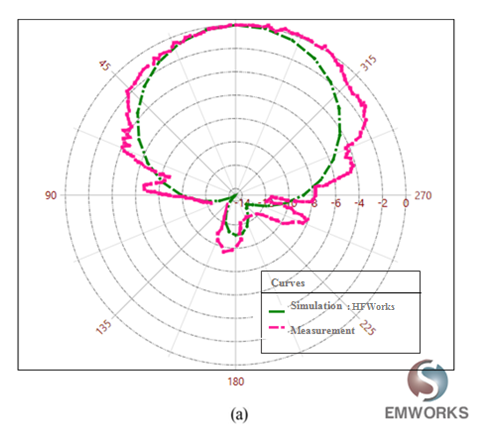

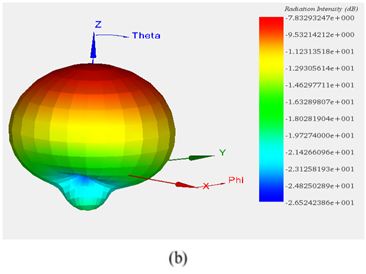

シミュレーション結果は、CPU モデルに取り付けられたヒートシンクの有無にかかわらず調査されます。ヒートシンクなしの場合、共振周波数は、ポート 1 で反射係数 -11.45 dB および 4.9 GHz -20.54 dB の 2.05 GHz で検出され、ポート 1 で反射係数 -4.32 dB の 2.05 GHz および反射係数 -18.83 dB の 4.9 GHz で検出されます。 2. ヒートシンクが CPU に取り付けられている場合、共振周波数は、ポート 1 で反射係数 -25.83 dB の 2.3 GHz と反射係数 -12.90 dB の 5.45 GHz、および反射係数 -3.41 dB の 2.3 GHz で検出されます。図 4 に示すように、HFWorks の結果は測定データに近くなっています。 2.05 GHz での遠方界の結果が図 5 に示され、ここでも測定データとの良好な比較が示されています。

図 4 - (a) ポート 1 での反射係数。 (b) ポート 2 での反射係数。

図 5 - (a) 2.05 GHz での放射パターンの 2D プロット、(b) 2.05 GHz での放射パターンの 3D プロット

B. ヒートシンクの高さ

図 3 に示すように、ヒートシンクはフィンのない固体ブロックとして簡略化されています。フィールドおよび回路結果に対するヒートシンクの高さの影響を研究し、ヒートシンク付きデュアル ダイ CPU の最適化された構造を得るために、さまざまなシミュレーションが実行されました。表 1 に示すように、ポート 1 とポート 2 の両方で、ヒートシンクの高さが反射係数に与える影響は最小限です。したがって、Intel デュアル ダイ CPU の共振周波数と散乱パラメータは、搭載されているものではなく、内部構造に大きく依存します。

シミュレーション設定 HFW (Port1) | 反射係数 | |

| GHz | dB | |

Height of Heatsink HH=37mm | 1.75 | -16.69169 |

| 5.525 | -6.11 | |

Height of Heatsink HH=42mm | 1.75 | -16.74 |

| 5.525 | -6.09 | |

Height of Heatsink HH=47mm | 1.75 | -25.28 |

| 5.525 | -11.21 | |

シミュレーション設定 HFW (ポート 2) | 反射係数 | |

| GHz | dB | |

Height of Heatsink HH=37mm | 1.75 | -8.91 |

| 5.525 | -20.2224 | |

Height of Heatsink HH=42mm | 1.75 | -11.38 |

| 5.525 | -13.10 | |

Height of Heatsink HH=47mm | 1.75 | -11.42 |

| 5.525 | -12.25 | |

C. 熱シミュレーション

図 6 は、モデル化された構造の導体損失と誘電損失による CPU 内の温度分布を示しています。