説明

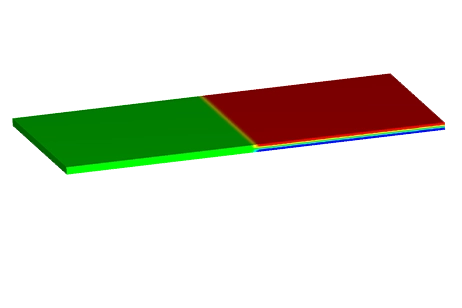

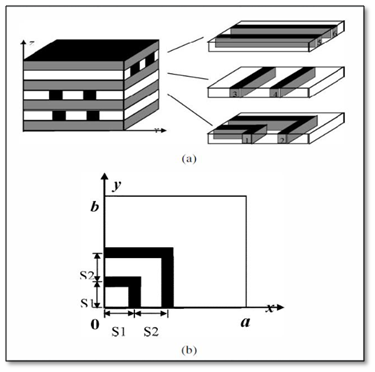

この検証例では、7 つの誘電体層に埋め込まれた 6 つの導体で構成される相互接続の静電容量を計算する方法を示します。図 1 に示すように、6 つの導体のうち 4 つが 2 つの 90 度の屈曲部を横切っています。

図 1 - 7 つの誘電体層のセットに埋め込まれた 6 つの導体

各直線導体の長さは 13mm です。すべての導体の断面は 1mm × 1mm です。図 1 に示すように、曲げ導体の分割長は a=b=13mm、S1=3.5mm、S2=3mm です。誘電体層の比誘電率は、下から、e r1=2、e r2=3、e r3=3、e r4=4、e r5=4、e r6=5、e r7=5です。

下から3番目の層を除いて、各層の厚さは1mmです。 2mmの厚みがあります。構造体の全高は8mm。構造物周辺の空気もモデルに含める必要があります。公開された記事では、ドメイン分解法 (DDM) が、考慮されている相互接続の静電容量計算機として使用されています。キャパシタンス計算のために公開されたデータ [1] に対して EMS の結果を検証したいと考えています。

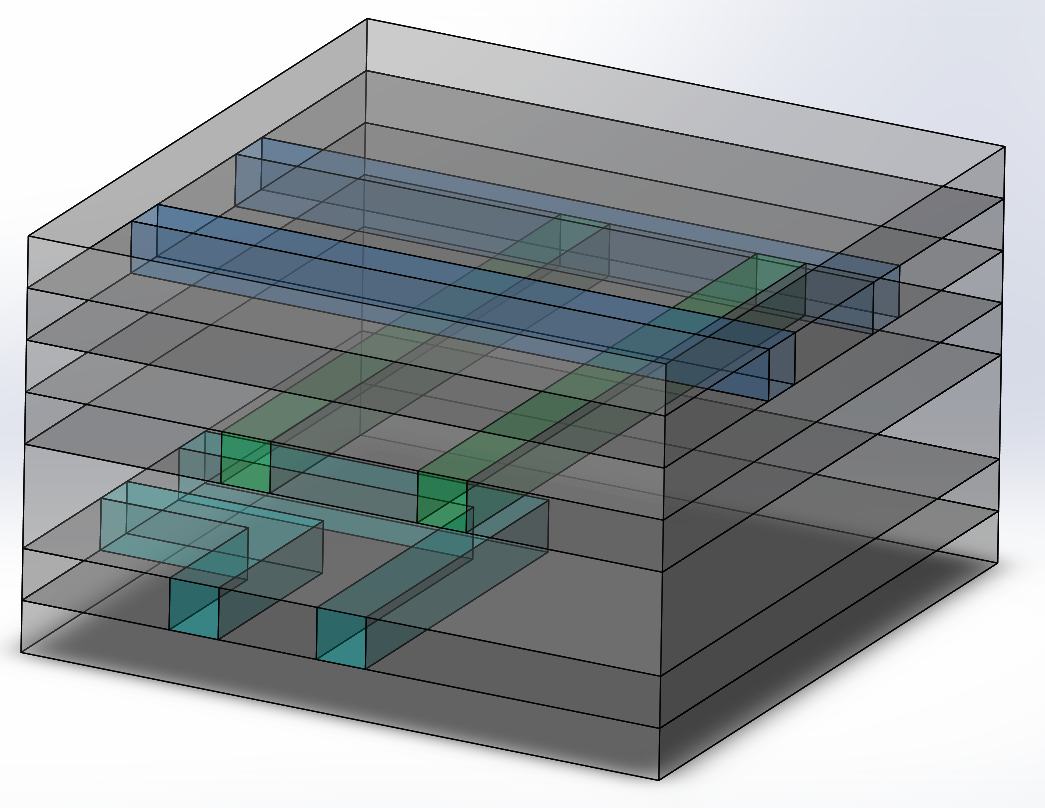

図 2 - 7 層相互接続のソリッド モデル

スタディ

EMS の静電モジュールは、手元の 3D 多層配線構造の静電容量計算ツールとして使用されます。 EMS で静電スタディまたは設計シナリオを作成した後、常に 3 つの重要な手順に従う必要があります。つまり、すべてのソリッド ボディに適切な材料を適用し、必要な境界条件、または EMS のいわゆる荷重/拘束を適用し、モデル全体をメッシュ化します。

材料

EMS の静電解析で必要な唯一の材料特性は比誘電率です。これは、7 つの絶縁体と周囲の空気について表 1 に示されています。

コンポーネント/ボディ | 材料名 | 比誘電率 |

Air | 空気 | 1.0 |

Dielectric 1 | e2 | 2.0 |

Dielectric 2 | e3 | 3.0 |

Dielectric 3 | e3 | 3.0 |

Dielectric 4 | e4 | 4.0 |

Dielectric 5 | e4 | 4.0 |

Dielectric 6 | e5 | 5.0 |

Dielectric 7 | e5 | 5.0 |

表 1 - 7 つの絶縁体と周囲の空気の比誘電率

負荷/制約

モデルの電気環境と磁気環境を定義するには、荷重と拘束が必要です。解析結果は、指定された荷重と拘束に直接依存します。荷重と拘束は、ジオメトリに完全に関連付けられ、ジオメトリの変更に自動的に調整されるフィーチャとしてジオメトリ エンティティに適用されます。

このスタディでは、接地された導体が、それぞれ第 7 層と第 1 層の誘電体層の上面と下面に適用されます。 EMS では、いわゆるフローティング導体を使用して、導体にインデックスが付けられます。つまり、番号が付けられます。

メッシング

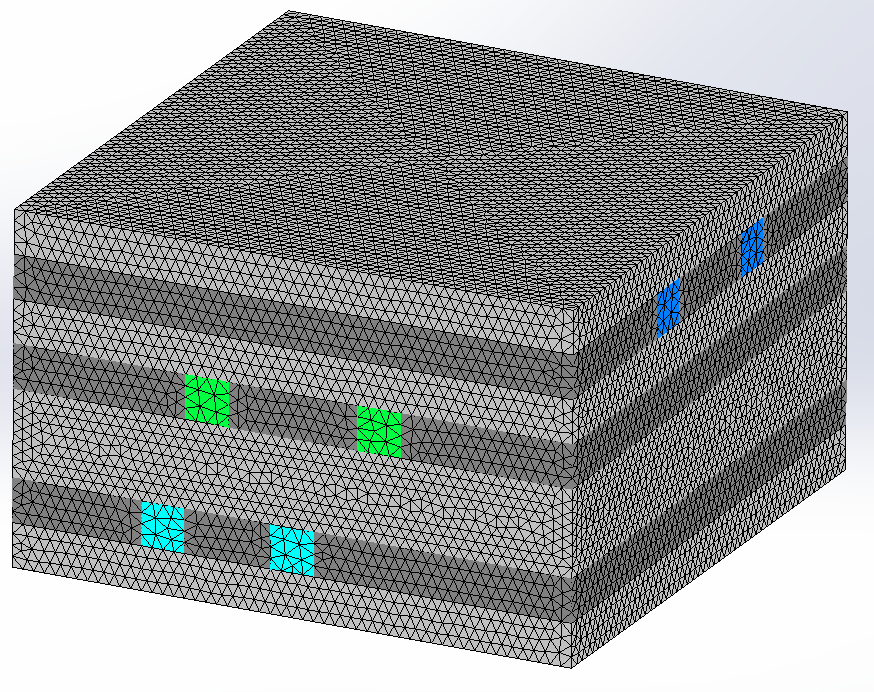

図 3 -空気領域のない構造のメッシュ

結果

実行が成功すると、静電モジュールは 3 つの結果フォルダーと結果テーブルを生成します。フォルダには、それぞれ電場 E、電気変位 D、電位分布 V が含まれています。結果テーブルには静電容量マトリックスが含まれています。さらに、すべての結果は、フリンジ、ベクトル、等高線、セクション、ライン、およびクリッピング プロットなどのさまざまな形式で視覚化できます。結果は簡単に拡大、エクスポート、分析できます。

この特定のベンチマークでは、キャパシタンス マトリックスが [1] で報告された結果と比較されます。表 2 が示すように、EMS の結果は [1] の著者によって報告されたものと一致します。 EMS は、相互接続および VLSI のキャパシタンス カリレータと考えることができます。

C ij (pF) | conductor-1 | conductor-2 | conductor-3 | conductor-4 | conductor-5 | conductor-6 |

conductor-1 | 0.745 | -0.158 | -0.123 | -6.515 e-03 | -2.807 e-02 | -4.566 e-03 |

conductor-2 | -0.158 | 1.369 | -0.210 | -0.145 | -3.278 e-02 | -2.885 e-02 |

conductor-3 | -0.123 | -0.210 | 1.743 | -0.172 | -0.256 | -0.262 |

conductor-4 | -6.516 e-03 | -0.145 | -0.172 | 1.689 | -0.265 | -0.267 |

conductor-5 | -2.807 e-02 | -3.277 e-02 | -0.256 | -0.265 | 3.469 | -5.154 e-02 |

conductor-6 | -4.566 e-03 | -2.885 e-02 | -0.262 | -0.267 | -5.154 e-02 | 3.448 |

表 2 - EMS によって得られたキャパシタンス マトリックス (pF)

C11 | し22 | し33 | し44 | C55 | し66 | |

DDM | 0.680 | 1.29 | 1.57 | 1.52 | 2.54 | 2.54 |

Spice Link | 0.669 | 1.29 | 1.60 | 1.54 | 2.53 | 2.53 |

表 3 - [1] で報告されている自己容量項 (pF)

参考文献

[1] Zhenhai Zhu, Hao Ji, Wei Hong, "An Efficient Algorithm for the Parameter Extraction of 3-D Interconnect Structures in the VLSI Circuits: Domain-Decomposition Method," IEEE Transactions on Microwave Theory and Techniques, vol. 45, no. 8, August 1997, pp. 1179-1184.